時間でコントロールするLTspiceのツールを作ろうと思います。

たとえば、電源のあるなしとか信号の有無で回路の動作を比較しようと思ったときに、それらをスイッチで切り換えることができたら便利だと思います。

また、抵抗の値を時系列で変化させることができれば、効果的な回路評価ができるだろうと思います。

※ 第1の方法

【LTspice】サブサーキットの作成方法と使用方法について

サブサーキットの作成方法 以下の順番で行うと、サブサーキットを作成し使用することができます。 サブサーキットの回路図ファイル(*.ascファイル)を作成する。 サブサーキットのシンボルファイル(*.a

- サブサーキットの回路図ファイル(xyz.asc)を作成する。

- これと同じ名前のサブサーキットのシンボルファイル(xyz.asy)を作成する。

- 回路図ファイルとシンボルファイルをパスの通ったシンボルファイル用のフォルダに置く。

- あるいは、2つのファイルを親回路図ファイルと同じフォルダに置く。

※ 第2の方法

- サブサーキットの回路図ファイル(xyz.asc)から、ライブラリファイル(xyz.cir)を作成する。

- シンボルファイル(xyz.asy)の項目にライブラリファイル(xyz.cir)を設定する。

ON/OFFスイッチ

電圧制御スイッチと電圧をpulseで変化させる電圧源を使えば、下図のように所望の時間で回路の遮断ができます。これをサブサーキット化して便利に使えるスイッチを作るのが目的です。

- 赤枠で囲んだ部分をモデル定義を含めてサブサーキットの回路図ファイル(*.asc)にします。

- サブサーキットを摸式化したシンボルファイル(*.asy)をつくります。

- スイッチをON/OFFする時間は親回路で調整できるようにします。

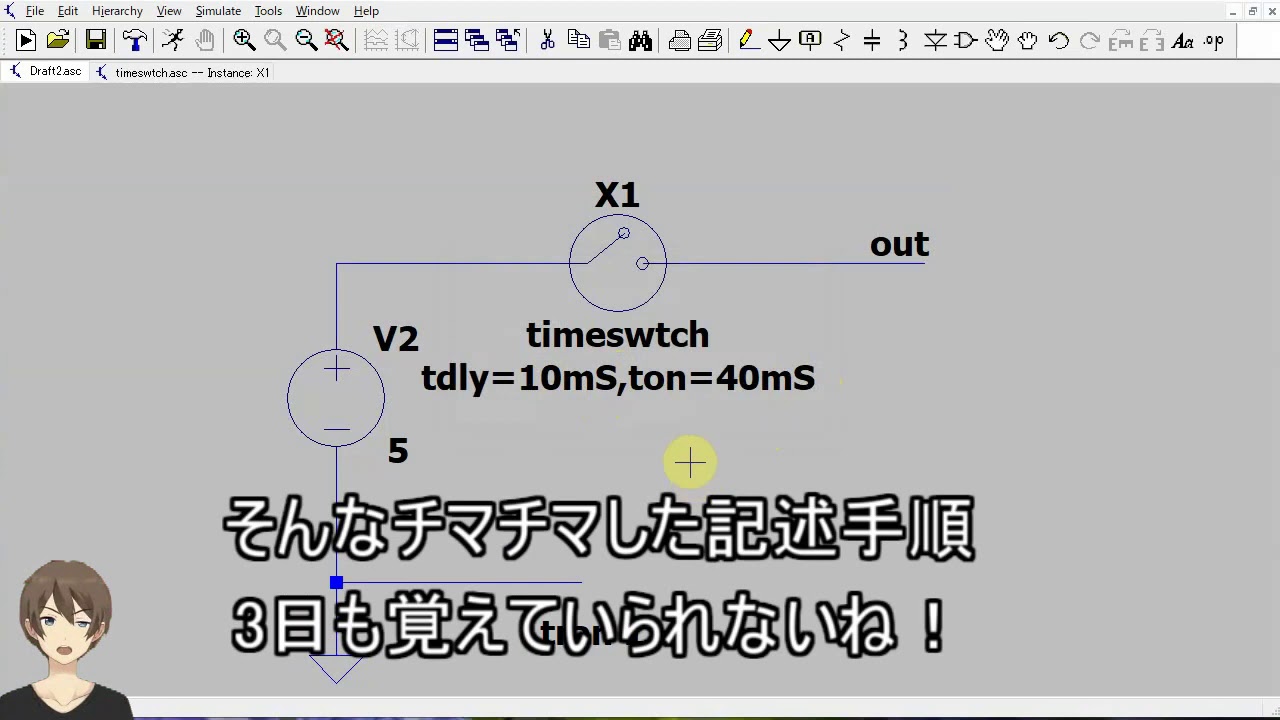

主回路図に表示するのはシンボルで、その裏でサブサーキットが動いているという仕組みです。ON/OFF時間の設定はパラメータで行い、それは主回路図から変更します。

ノーマルオープン・スイッチ

- サブサーキットの回路図作成

- サブサーキットのシンボル作成

- 調整パラメータ記述

1. サブサーキットの回路図作成

まず、左図のサブサーキット回路を描きます。ファイル名は noSW.asc とします。

S1は電圧制御スイッチで、

.model モデル名 SW(High設定 Low設定 閾値Vt ヒスVh)

のフォーマットです。すなわち、入力HighのときはRon=1mΩで、入力LowのときはRoff=1TΩの抵抗を持つスイッチになります。またHigh/Low入力は0.5Vを閾値として切り換わります。このときのヒステリシスはゼロです。

V1は電圧スイッチを動かすDC電源で、

初期値0Vで、Tdeley経過後に1Vになり、Ton継続します。

|

| 左図:NO回路のサブサーキット noSW.asc 右図:シンボル noSW.asy |

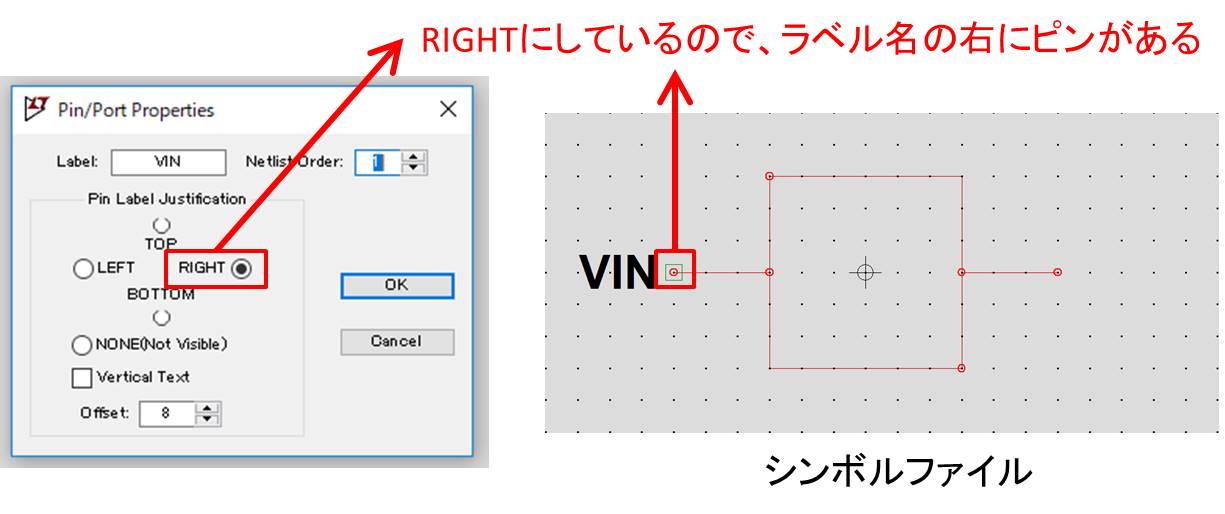

2. サブサーキットのシンボル作成

3. 調整パラメータ記述

つぎに、親回路からスイッチをON/OFFする時間を変更できるように設定します。

- シンボルファイルの上でマウスを右クリックして、"Attributes"から、"Edit Attributes" を選びます。左下図のように”SpiceLine” 項目に Tdeley=1m Ton=5m を書き入れます。

- 同じく、シンボルファイルの上でマウスを右クリックして、"Attributes"から、"Attributes Window" を選びます。右下図のように”SpiceLine” 項目をクリックしてシンボル図上に置きます。

|

| 左図:Edit Attributes 右図 Attributes Window |

ノーマルクローズ・スイッチ

同じようにして、ノーマルクローズのスイッチも作りました。違いはRonとRoffの定義を入れ替えたことと、接点が接触しているシンボルにしたことです。

|

| 左図:NC回路のサブサーキット ncSW.asc 右図:シンボル ncSW.asy |

動作確認と参照元

【伝スパ】LTSpiceのためのタイムスイッチを作ろう その6

タイムスイッチをもう少し便利に......タイムスイッチを作ろう シリーズの改定動画です。サンプル回路【伝スパ】タイムスイッチを作ろう.ziphttps://drive.google.com/file/d/15VImFcIc-jULELvYBLwKfj-li9qiUN2s/view?usp=sharing#LTS...

可変抵抗

抵抗値は電源V1の出力電圧値:R=V(V1) で表しています。V(V1)を無次元化するとかの工夫がいるかと思いましたが、この式で(とりあえず)問題なく動いています。

親回路に引き渡すパラメータは、抵抗の変化の始まりを定義する Tdeley, R1 と終わりを定義する Tramp, R2 の4つです。

0ΩだとLTspiceが拒否するので、R1、R2には1mΩを加えています。

R1 > R2 のケース(青色)では、切り換わりの始まりで抵抗の変化がだれているのですが、原因不明です。

ポテンシオメータ

上図に示すポテンシオメータ(ボリューム)で、時間に応じて抵抗の分割比を変化させます。電圧制御電源の出力 wip は抵抗の分割比率を表し、PWLで0から1まで変化します。このとき、分割された抵抗は全抵抗をRtot として、下図のなかの数式のように書けます。

この回路図を前例に倣ってシンボル化すればサブサーキット化できます。

下記に引用元を示します。考え方は前項で私が作ったものと同じですが、ポテンシオの抵抗分割比を変化させるコントロール電圧源をサブサーキットから外に出しています。これによって、抵抗分割比の変化のさせ方を色々できるようになります。電圧源のメニューに出てくる波形のすべてが利用できると思います。

EEVblog Electronics Community Forum »Electronics »Beginners »Seeking help with LTspice simulation of Variable Power Supply

potentiometerVC is voltage controlled with the wiper position set by a control voltage in the range 0 to 1V, with respect to the circuit universal ground node 0. Simply ground the control voltage source's negative terminal, drop a net label on its positive terminal, and the same net label on the potentiometerVC's control terminal (far end of dotted line opposite wiper). Its total track resistance is set by the instance parameter Rtot.

ポテンショメータ VC は、0 ~ 1 V の制御電圧によってワイパー位置を決めます。全抵抗はパラメータ Rtot によって設定されます。

Both limit the effective wiper position to the range 0.001 to 0.999 as the LTspice SPICE engine cant handle resistances actually going to zero. When the wiper position is zero, its at the bottom end of the track if the symbol hasn't been rotated.

LTspice SPICE エンジンは実際にゼロになる抵抗を処理できないため、どちらも有効なワイパー位置を 0.001 から 0.999 の範囲に制限します。ワイパーの位置がゼロの場合、シンボルが回転していない場合はトラックの下端になります。

ためしに、制御電圧電源の出力 VCとして、左図は振幅±0.5Vのサイン波をスイープさせたものと、右図はこのぎり波(振幅0.1V)にしたものをつくってみました。

PotentiometerVRは主回路図で抵抗の変化のさせ方を決めれるので、汎用性があります。ただし、注意点が2つあります。

1点目は、上記の回路図に赤色でマーキングしていますが、サブサーキットの制御電圧と主回路の制御電圧VCを繋げる必要があります。つまり、主回路の電源出力ラベル(VC)と同じラベル(VC)を呼び出したサブサーキットの点(x)に付けねばなりません。

上記のためし事例では、のこぎり波の振幅は0.1Vなので、全抵抗10kΩの上限10% $(\frac{0.1}{1.0})$ で部分的に変化しています。

作ったサブサーキットの .cirファイル化

自作サブサーキットは回路図ファイル .asc とシンボルファイル .asy を同じフォルダに置いて使うことが使用条件です。普通、外部から入手するモデルの場合は、入手できるのはモデルを定義したライブラリファイル .lib, .sub などで、これは \libフォルダに置きます。そして、対応するシンボルファイルを作成して \symフォルダに置きます。

今まではこの整理の仕方に慣れていたので、同じフォルダに置く自作サブサーキットの使い方の方に抵抗がありました。そこで、.cirライブラリ化すると何が違うのか知りたくなりました。回路図ファイル .asc から .cir (.subと同じらしい)を作る方法があるので、試してみることにします。

ポテンシオメータの potVR.asc を使ってやってみます。

potVR.asc の上でマウス右クリックして、”View”から、”Spice Netlist” を選ぶと、下図右のネットリストが出てきます。さらに、ネットリスト上で右クリックして、”Edit as independent Netlist” を選んで、potVR.cir の名前で保存します。

元の potVR.asc は黒背景です。NetListから作った potVR.cir はグレー背景です。緑文字はコメントで、お決まりの手順どおり2か所の赤文字部分を追加しています。親回路とシンボルを繋ぐポート番号と制御電圧の情報、それにパラメータ情報だけに絞り込まれたものが .cir になっています。

出来上がった potVR.cir はシンボルファイルのフォルダからライブラリフォルダに移動して使います。

サブサーキットを呼び出した親回路とシンボル上で右クリックして、”Attribute” から、”Prefix”を”X”にします。

自作サブサーキットを .cir 化するのは手間がかかるばかりで、メリットは感じられません。デメリットは .cir 化するとビジアルなサブサーキット回路図情報がなくなります。現時点の私のLTspiceの使い方で考えたら、サブサーキット回路図を目で見て確認する使い方になると思うので、.cir 化しないことにします。